Add to Cart

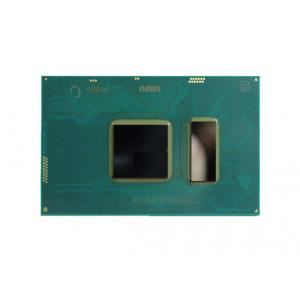

Série de la puce de processeur d'unité centrale de traitement du noyau I3-6100U SR2EU I3 (3MB cachette, jusqu'à 2.3GHz) - unité centrale de traitement de carnet

Le noyau i3-6100U est un double-noyau SoC d'ULV (tension très réduite) basé sur l'architecture de Skylake et a été lancé en septembre 2015. L'unité centrale de traitement peut être trouvée dans les ultrabooks aussi bien que des carnets normaux. En plus de deux noyaux d'unité centrale de traitement avec le Hyper-filetage synchronisé à 2,3 gigahertz (aucun Turbo Boost), la puce intègre également HD Graphics 520 GPU et un contrôleur à canal double de la mémoire DDR4-2133/DDR3L-1600. Le SoC est fabriqué utilisant un processus de 14 nanomètre avec des transistors de FinFET.

| Nombre de processeur | i3-6100U |

| Famille | Mobile du noyau i3 |

| Technologie (micron) | 0,014 |

| Vitesse du processeur (gigahertz) | 2,3 |

| Taille de la cachette L2 (KBs) | 512 |

| Taille de la cachette L3 (mb) | 3 |

| Le nombre de noyaux | 2 |

| EM64T | Soutenu |

| Technologie de HyperThreading | Soutenu |

| Technologie de virtualisation | Soutenu |

| Technologie augmentée de SpeedStep | Soutenu |

| Caractéristique mordue pardébronchement | Soutenu |

Informations générales :

| Type | Unité centrale de traitement/microprocesseur |

| Segment de marché | Mobile |

| Famille | |

| Numéro de type | |

| Numéro de la pièce d'unité centrale de traitement |

|

| Fréquence | 2300 mégahertz |

| Multiplicateur d'horloge | 23 |

| Paquet | 1356-ball micro-FCBGA |

| Prise | BGA1356 |

| Taille | 1,65 » x 0,94"/4.2cm x 2.4cm |

| Date d'introduction | 1er septembre 2015 (annonce) 1er septembre 2015 (disponibilité en Asie) 27 septembre 2015 (disponibilité ailleurs) |

Architecture Microarchiteture :

| Microarchitecture | Skylake |

| Noyau de processeur | Skylake-U |

| Creusez la progression | D1 (SR2EU) |

| Processus de fabrication | 0,014 microns |

| Largeur de données | bit 64 |

| Le nombre de noyaux d'unité centrale de traitement | 2 |

| Le nombre de fils | 4 |

| Unité de virgule flottante | Intégré |

| Taille de niveau 1 cachette | 2 x 32 la manière du KB 8 a placé les cachettes associatives d'instruction 2 x 32 la manière du KB 8 a placé les cachettes associatives de données |

| Taille de niveau 2 cachettes | 2 x 256 la manière du KB 4 a placé les cachettes associatives |

| Taille de niveau 3 cachettes | 3 la manière du mb 12 a placé la cachette partagée associative |

| Mémoire physique | 32 GIGAOCTETS |

| Multitraitement | Non soutenu |

| Prolongements et technologies |

|

| Caractéristiques de puissance faible | Technologie augmentée de SpeedStep |

Périphériques/composants intégrés :

| Contrôleur d'affichage | 3 affichages |

| Graphiques intégrés | Type de GPU : HD 520 Rangée de graphiques : GT2 Microarchitecture : GEN 9 LP Modules exécution : 24 Fréquence basse (mégahertz) : 300 Fréquence maximum (mégahertz) : 1000 |

| Contrôleur de mémoire | Le nombre de contrôleurs : 1 Canaux de mémoire : 2 Mémoire soutenue : LPDDR3-1600, LPDDR3-1866, DDR4-1866, DDR4-2133 Largeur de bande maximum de mémoire (GB/s) : 34,1 |

| D'autres périphériques |

|

Paramètres électriques/thermiques :

| Température de fonctionnement maximum | 100°C |

| Thermal Design Power | 15Watt |