Add to Cart

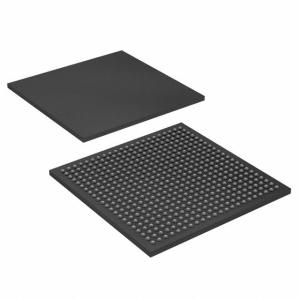

Réseau prédiffusé programmable de logique d'EP3C55F484C8N EP3C55U484I7N de champ programmable d'ICS FPGA - cyclone III 3491 IOS des laboratoires 327

Architecture de famille de dispositif du cyclone III

La famille de dispositif du cyclone III inclut une caractéristique client-définie réglée qui est optimisée pour des applications portatives et offre un large éventail de densité, de mémoire, de multiplicateur inclus, et d'options d'entrée-sortie. La famille de dispositif du cyclone III soutient les nombreuses interfaces externes de mémoire et les protocoles d'entrée-sortie qui sont communs dans des applications fort débit. Les caractéristiques de logiciel de Quartus II et les noyaux parameterizable d'IP la faciliter pour que vous employiez les interfaces et les protocoles de famille de dispositif du cyclone III.

Les sections suivantes fournissent un aperçu des caractéristiques de famille de dispositif du cyclone III.

Blocs d'éléments logiques et de rangée de logique

Le bloc de rangée de logique (LABORATOIRE) se compose de 16 éléments logiques et d'un bloc de gestion de la taille du laboratoire. Un le est la plus petite unité de la logique dans l'architecture de famille de dispositif du cyclone III. Chaque le a quatre entrées, une table de consultation de quatre-entrée (LUT), un registre, et la logique de sortie. La quatre-entrée LUT est un générateur de fonction qui peut mettre en application n'importe quelle fonction avec quatre variables.

Blocs de mémoire

Chaque bloc de mémoire de M9K de la famille de dispositif du cyclone III fournit neuf Kbits de la mémoire de sur-puce capable du fonctionnement jusqu' 315 mégahertz pour des dispositifs du cyclone III et jusqu' 274 mégahertz pour des dispositifs du cyclone III LS. La structure de mémoire incluse se compose des colonnes de blocs de mémoire de M9K que vous pouvez configurer comme RAM, les premiers- tampons (fifo) système premier entré, premier sorti, ou la ROM. Les blocs de mémoire de famille de dispositif du cyclone III sont optimisés pour des applications telles que la haute dans tout le traitement de paquet, le programme inclus de processeur, et le stockage de données inclus.

Le logiciel de Quartus II te permet de tirer profit des blocs de mémoire de M9K en instanciant la mémoire utilisant un magicien consacré de megafunction ou en impliquant la mémoire directement du code source de VHDL ou de Verilog.

Simple-port de soutien de blocs de mémoire de M9K, modes d'opération double accès double accès et et véritables simples. le mode de Simple-port et le mode double accès simple sont soutenus pour toutes les largeurs gauches avec une configuration de ×1, de ×2, de ×4, de ×8, de ×9, de ×16, de ×18, de ×32, et de ×36. double accès vrai est soutenu dans les largeurs gauches avec une configuration de ×1, de ×2, de ×4, de ×8, de ×9, de ×16, et de ×18.