Add to Cart

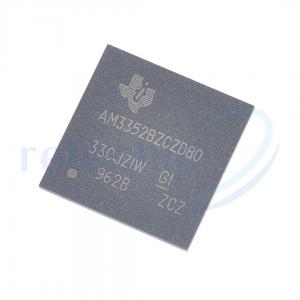

AM3352BZCZD80 MPU ARM Cortex-A8 32Mbit 800 MHz 1,26V PBGA-324

Caractéristiques

• Processeur RISC 32 bits A8 jusqu' 1 GHz avec le système de traitement SitaraTM ARM® Cortex®

32KB d'instruction L1 et 32KB de cache de données avec détection d'erreur unique (parité)

256KB de cache L2 avec code de correction d'erreur (ECC)

176KB de ROM de démarrage sur puce

64KB de RAM dédiée

Émulation et débogage - JTAG

¢ Contrôleur d'interruption (jusqu' 128 demandes d'interruption)

• Mémoire sur puce (RAM L3 partagée)

64 Ko de mémoire vive pour contrôleur de mémoire sur puce usage général (OCMC)

¢ Accessible tous les maîtres

¢ Prend en charge la rétention pour un réveil rapide

• Interfaces de mémoire externe

Le contrôleur de l'appareil doit être configuré de manière ce que le système de contrôle de l'appareil puisse fonctionner correctement.

¢ mDDR: Horloge de 200 MHz (débit de données de 400 MHz)

DDR2: Horloge de 266 MHz (débit de données de 532 MHz)

¢ DDR3: Horloge 400 MHz (débit de données 800 MHz)

¢ DDR3L: Horloge 400 MHz (débit de données 800 MHz)

¢ Bus de données 16 bits ¢ 1 Go d'espace d'adressage total

Prend en charge une configuration de périphérique de mémoire x16 ou deux x8

¢ Contrôleur de mémoire usage général (GPMC)

Interface de mémoire asynchrone flexible 8 bits et 16 bits avec jusqu' sept sélections de puces (NAND, NOR, Muxed-NOR, SRAM)

Utilise le code BCH pour prendre en charge l'ECC 4, 8 ou 16 bits

Utilise le code Hamming pour prendre en charge l'ECC 1 bit

Module de localisation des erreurs (ELM)

Utilisé conjointement avec le GPMC pour localiser les adresses des erreurs de données partir de polynômes de syndrome générés l'aide d'un algorithme BCH

Prend en charge la localisation des erreurs de blocage de 4, 8 et 16 bits par bloc de 512 octets basé sur les algorithmes BCH

• Sous-système d'unité en temps réel programmable et sous-système de communication industrielle (PRU-ICSS)

Il prend en charge des protocoles tels qu'EtherCAT®, PROFIBUS, PROFINET, EtherNet/IPTM et plus encore.

Deux unités programmables en temps réel (UPR)

Processeur RISC charge/stockage de 32 bits, capable de fonctionner 200 MHz

8KB de RAM d'instruction avec détection d'erreur unique (parité)

8KB de mémoire vive de données avec détection d'erreur unique (parité)

¢ Multiplicateur 32 bits cycle unique avec accumulateur 64 bits

Le module GPIO amélioré fournit un support de changement d'entrée/sortie et un verrouillage parallèle sur le signal externe

12KB de RAM partagée avec détection d'erreur unique (parité)

Trois banques de registres de 120 octets accessibles chaque UPR

¢ Contrôleur d'interruption (INTC) pour le traitement des événements d'entrée du système

Bus d'interconnexion local pour connecter les maîtres internes et externes aux ressources l'intérieur du PRU-ICSS

Les périphériques l'intérieur du PRU-ICSS: Un port UART avec des broches de contrôle de débit, prenant en charge jusqu' 12 Mbps

¢ Un module de capture améliorée (eCAP)

Deux ports Ethernet MII qui prennent en charge l'Ethernet industriel, comme EtherCAT

Un port MDIO • Module de gestion de l'alimentation, de la réinitialisation et de l'horloge (PRCM)

Contrôle l'entrée et la sortie des modes de veille et de sommeil profond

Il est responsable de la séquence de sommeil, de la séquence de désactivation du domaine d'alimentation, de la séquence de réveil et de la séquence d'allumage du domaine d'alimentation.

¢ Horloges

Ossillateur haute fréquence intégré de 15 35 MHz utilisé pour générer une horloge de référence pour divers systèmes et horloges périphériques

Il prend en charge le contrôle individuel de l'horloge pour activer et désactiver les sous-systèmes et les périphériques afin de réduire la consommation d'énergie.USB et périphériques [MMC et SD], UART, SPI, I 2C], L3, L4, Ethernet, GFX [SGX530], Horloge pixels LCD

Diagramme de blocage fonctionnel

Les spécifications

| Attribut du produit | Valeur attribuée |

|---|---|

| 32 bits | |

| 800 MHz | |

| Les produits de la catégorie 1 | |

| 32 kB | |

| 32 kB | |

| 1.26 V | |

| Le système de détection de l'émission | |

| - Quarante degrés | |

| + 125 °C | |

| Taille de la mémoire RAM: | 64 kB, 64 kB |

| Taille de la ROM: | 176 kB |

| Kit de développement: | Le numéro de téléphone: |

| Voltage d'entrée/sortie: | 10,8 V, 3,3 V |

| Type d'interface: | Pour les appareils électroniques électroniques: |

| Instruction de cache L2 / mémoire de données: | 256 kB |

| Type de mémoire: | L1 / L2 / L3 Cache, RAM, ROM |

| Sensible l'humidité: | - Oui, oui. |

| Nombre de compteurs: | Températeur 8 |

Guides commerciaux

| Transport aérien | Période de livraison | Pour les pièces en stock, les commandes devraient être expédiées

dans 3 jours. Une fois expédié, le délai de livraison estimé dépend des transporteurs ci-dessous que vous avez choisis: DHL Express, 3 7 jours ouvrables. DHL eCommerce, 12 22 jours ouvrables. Priorité internationale de FedEx, de 3 7 jours ouvrables EMS, 10-15 jours ouvrables. Courrier aérien, 15 30 jours ouvrables. |

| Tarifs de livraison | Après avoir confirmé la commande, nous évaluerons le coût d'expédition en fonction du poids des marchandises | |

| Option d'expédition | Nous fournissons la livraison internationale par DHL, FedEx, EMS, SF Express et par courrier aérien enregistré. | |

| Suivi des expéditions | Nous vous informerons par e-mail avec le numéro de suivi une fois la commande expédiée. | |

Retour garantie | Retour | Les retours sont normalement acceptés lorsqu'ils sont effectués dans les 30 jours suivant la date d'expédition.Les pièces doivent être inutilisées et dans leur emballage d'origine.Le client doit prendre en charge l'expédition. |

| Garantie | Tous les achats de Retechip sont assortis d'une politique de remboursement de 30 jours. Cette garantie ne s'applique pas tout article dont les défauts ont été causés par un assemblage inapproprié du client,non-respect par le client des instructions, modification du produit, utilisation négligente ou incorrecte | |

| Commande |

Paiement

| T/T, PayPal, carte de crédit incluent Visa, Master, American Express. |